# VMAX: A VIRTUAL MACHINE FOR THE PCMAX2

Version 2.00

1990 July 16

Roger House Everex Sebastopol R&D 707-823-0733

# Table of Contents

|                                                                                                                                                                                                                                                                                                                                                                                   | page                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                                                                    |

| Design Criteria                                                                                                                                                                                                                                                                                                                                                                   | 7                                                                                                                    |

| VMAX Memory and Address Space                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                                                    |

| Operand Types                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                                   |

| VMAX Registers<br>General Registers<br>Stack Pointer<br>Frame Pointer<br>Program Counter<br>Flags Register                                                                                                                                                                                                                                                                        | 12<br>13<br>13<br>15<br>18<br>19                                                                                     |

| Addressing Modes                                                                                                                                                                                                                                                                                                                                                                  | 21                                                                                                                   |

| Instruction Formats<br>General Considerations<br>Overview of Formats<br>The qr Format<br>The r-operand<br>The q-operand<br>Notation for qr Operands<br>Decoding the q-field<br>The qc Format<br>The qo Format<br>The qo Format<br>The ir Format<br>The ir Format<br>The i-operand<br>The j-operand<br>Notation for ij Operands<br>The b1 Format<br>The n0 Format<br>The n0 Format | 23<br>25<br>27<br>28<br>29<br>36<br>37<br>39<br>40<br>41<br>43<br>44<br>45<br>46<br>49<br>49<br>50<br>51<br>52<br>52 |

| Instruction Set Summary by Function<br>Data Movement Instructions<br>Move Instructions<br>Store Instructions<br>Load Address Instruction<br>Flags Instructions<br>Arithmetic Instructions<br>Add Instructions<br>Subtract Instructions<br>Multipy Instructions                                                                                                                    | 53<br>53<br>54<br>55<br>55<br>56<br>56<br>57<br>58                                                                   |

| Divide Instructions<br>Other Arithmetcic Instructions<br>Shift Instructions<br>Logical Instructions<br>Convert Instructions<br>Compare Instructions<br>Jump Instructions<br>Stack Instructions<br>Miscellaneous Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                   | 59<br>63<br>64<br>65<br>66<br>69<br>70<br>72<br>72                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Notation Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                   | 73                                                                                     |

| Instruction DescriptionsabsdAbsolute value of doubleabsfAbsolute value of floatabs1Absolute value of longabswAbsolute value of wordaddc1Add long with carryadddAdd floataddfAdd longaddlAdd longadduwlAdd word to longaddwAdd wordandlAnd word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                   | 76<br>77<br>78<br>79<br>79<br>80<br>80<br>81<br>81<br>81<br>82<br>82<br>83             |

| callCallCall backwardcallfCall forwardcmpdCompare doublecmpfCompare floatcmplCompare longcmplbCompare loworder byte of long tocmpwCompare loworder byte of word tocmpwbCompare loworder byte of word tocvtbslConvert byte sign-extended to JcvtbslConvert byte sign-extended to JcvtbslConvert byte zero-extended to JcvtbzwConvert byte zero-extended to JcvtbdfConvert float to doublecvtsldConvert signed long to doublecvttdslConvert truncated double to signcvttdslConvert truncated float to signcvttfulConvert trunc. float to unsigncvttfulConvert unsigned long to doublecvtudConvert unsigned long to floatcvtuldConvert unsigned long to floatcvtuldConvert unsigned long to floatcvtuldConvert unsigned long to floatcvtuldConvert unsigned long to floatcvtulfConvert unsigned long to float | to byte<br>to byte<br>long<br>word<br>word<br>word<br>gned long<br>ned long<br>ed long<br>ed long | 83<br>84<br>85<br>86<br>87<br>87<br>88<br>89<br>90<br>91<br>92<br>92<br>93<br>94<br>95 |

| cvtwzl<br>divd<br>divf<br>divrsl<br>divrsw<br>divrul<br>divrulw<br>divruw<br>divsl<br>divsw<br>divul<br>divuu                               | Convert word zero-extended to long<br>Divide double<br>Divide float<br>Divide with remainder signed long<br>Divide with rem. signed long by word<br>Divide with remainder signed word<br>Divide with remainder unsigned long<br>Divide with remainder unsigned long by word<br>Divide with remainder unsigned word<br>Divide signed long<br>Divide signed long<br>Divide unsigned long                                              | 95<br>96<br>97<br>97<br>98<br>98<br>99<br>99<br>100<br>100<br>101                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| enter                                                                                                                                       | Enter function                                                                                                                                                                                                                                                                                                                                                                                                                      | 102                                                                                                          |

| entersav                                                                                                                                    | Enter function and save registers                                                                                                                                                                                                                                                                                                                                                                                                   | 103                                                                                                          |

| gmov                                                                                                                                        | General move                                                                                                                                                                                                                                                                                                                                                                                                                        | 104                                                                                                          |

| gsto                                                                                                                                        | General store                                                                                                                                                                                                                                                                                                                                                                                                                       | 104                                                                                                          |

| halt                                                                                                                                        | Halt the VMAX machine                                                                                                                                                                                                                                                                                                                                                                                                               | 105                                                                                                          |

| jump<br>jumpb<br>jumpf                                                                                                                      | JumpJump backwardJump backwardJump forward                                                                                                                                                                                                                                                                                                                                                                                          | 105<br>106<br>106                                                                                            |

| leal                                                                                                                                        | Load effective address                                                                                                                                                                                                                                                                                                                                                                                                              | 107                                                                                                          |

| leave                                                                                                                                       | Leave function                                                                                                                                                                                                                                                                                                                                                                                                                      | 108                                                                                                          |

| leaveres                                                                                                                                    | Leave function and restore registers                                                                                                                                                                                                                                                                                                                                                                                                | 109                                                                                                          |

| movbl<br>movbw<br>movd<br>movf<br>movflags<br>movl<br>movw<br>movwl<br>muld<br>mulf<br>mulsl<br>mulsw<br>mulswl<br>mulswl<br>muluw<br>muluw | Move byte to loworder byte of long<br>Move byte to loworder byte of word<br>Move double<br>Move float<br>Move word to flags register<br>Move word<br>Move word<br>Move word of long<br>Move word to loworder word of long<br>Multiply double<br>Multiply float<br>Multiply signed long<br>Multiply signed word<br>Multiply signed word syielding long<br>Multiply unsigned word<br>Multiply unsigned word<br>Multiply unsigned word | 110<br>110<br>111<br>111<br>112<br>112<br>113<br>113<br>114<br>114<br>115<br>115<br>116<br>116<br>117<br>117 |

| negd                                                                                                                                        | Negate double                                                                                                                                                                                                                                                                                                                                                                                                                       | 118                                                                                                          |

| negf                                                                                                                                        | Negate float                                                                                                                                                                                                                                                                                                                                                                                                                        | 118                                                                                                          |

| negl                                                                                                                                        | Negate long                                                                                                                                                                                                                                                                                                                                                                                                                         | 119                                                                                                          |

| negw<br>nop<br>notl<br>notw                                                                                                                  | Negate word<br>No operation<br>Not long<br>Not word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 119<br>120<br>120<br>121                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| orl<br>orw                                                                                                                                   | Or long<br>Or word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 121<br>122                                                                                                          |

| popd<br>popf<br>popl<br>popregs<br>popw<br>pushd<br>pushf<br>pushl<br>pushregs<br>pushw                                                      | Pop double<br>Pop float<br>Pop long<br>Pop multiple registers<br>Pop word<br>Push double<br>Push float<br>Push long<br>Push multiple registers<br>Push word                                                                                                                                                                                                                                                                                                                                                                                                                               | 122<br>123<br>123<br>124<br>124<br>125<br>125<br>125<br>126<br>126<br>127                                           |

| remsl<br>remsw<br>remuu<br>ret<br>rlil<br>rliw<br>rll<br>rlw<br>rril<br>rriw<br>rri<br>rriw                                                  | Remainder signed long<br>Remainder signed word<br>Remainder unsigned long<br>Remainder unsigned word<br>Return from call<br>Rotate left immediate long<br>Rotate left immediate word<br>Rotate left long<br>Rotate left word<br>Rotate right immediate long<br>Rotate right immediate word<br>Rotate right immediate word<br>Rotate right long                                                                                                                                                                                                                                            | 127<br>128<br>129<br>130<br>131<br>131<br>132<br>132<br>133<br>133<br>134<br>134                                    |

| set0l<br>set0w<br>set1l<br>set1w<br>slil<br>sliw<br>sll<br>slw<br>sqrtd<br>sqrtf<br>srail<br>sraiw<br>sral<br>sraw<br>srlil<br>srliw<br>srll | <pre>Store condition(0) into long<br/>Store condition(0) into word<br/>Store condition(1) into long<br/>Store condition(1) into word<br/>Shift left immediate long<br/>Shift left immediate word<br/>Shift left long<br/>Shift left word<br/>Square root of double<br/>Square root of float<br/>Shift right arithmetic immediate long<br/>Shift right arithmetic long<br/>Shift right arithmetic long<br/>Shift right arithmetic long<br/>Shift right arithmetic word<br/>Shift right arithmetic word<br/>Shift right logical immediate word<br/>Shift right logical immediate word</pre> | 135<br>136<br>136<br>137<br>137<br>138<br>138<br>139<br>139<br>140<br>140<br>141<br>141<br>141<br>142<br>142<br>143 |

| <pre>srlw stod stof stoflags stol stolb stolw stow stow stowb subcl subd subf subl subswl subuwl subwul subw</pre> | Shift right logical word<br>Store double<br>Store float<br>Store flags register into word<br>Store long<br>Store loworder byte of long into byte<br>Store loworder word of long into word<br>Store loworder byte of word into byte<br>Store loworder byte of word into byte<br>Subtract long with carry<br>Subtract double<br>Subtract float<br>Subtract long<br>Subtract signed word from long<br>Subtract word | 143<br>144<br>145<br>145<br>146<br>146<br>147<br>147<br>147<br>148<br>148<br>149<br>149<br>150<br>150<br>151 |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| xorl                                                                                                               | Exclusive or long                                                                                                                                                                                                                                                                                                                                                                                                | 151                                                                                                          |

| xorw                                                                                                               | Exclusive or word                                                                                                                                                                                                                                                                                                                                                                                                | 152                                                                                                          |

| Appendix A: | Instructions Grouped by Format                | 153 |

|-------------|-----------------------------------------------|-----|

| Appendix B: | Instructions Grouped by Function              | 161 |

| Appendix C: | Instructions Ordered Alphabetically by Opcode | 168 |

| Appendix D: | Differences Between VMAX v1.00 and v2.00      | 172 |

| Appendix E: | Ideas and Notes for Future Versions           | 177 |

| Appendix F: | Diagrams of Instruction Formats               | 181 |

## VMAX: A Virtual Machine for the PCMAX2

#### Introduction

VMAX is one component of a system which will allow a programmer to compile and execute C programs on a PCMAX2 board on a PC running DOS. This system is based on a C compiler, GCC, which can be tailored to generate code for most any 32-bit machine that addresses 8-bit bytes and has several general registers.

Since the PCMAX2 has a rather small code space (the Writable Control Store or WCS) and a rather small data space (the DataRam), it is not feasible to tailor GCC to generate PCMAX2 microcode. Instead, GCC is tailored to generate code for a virtual computer, the VMAX, which is then executed on the PCMAX2 by an interpreter which simulates the VMAX.

This document describes the architecture of VMAX: The address space, register structure, instruction formats, and detailed actions of all instructions. The intention is that this document should provide a complete and detailed description of VMAX which contains all the information needed for a programmer to write a VMAX interpreter.

Although VMAX is a general-purpose computer which could be described independently of both the PCMAX2 and GCC, it does not seem to be a good idea to treat VMAX as if if exists in a vacuum. The only reason the VMAX computer has been designed is so that GCC can be ported to the PCMAX2. Thus, both GCC and the PCMAX2 are mentioned frequently in this document.

#### Design Criteria

The design of the VMAX architecture was driven by two major requirements:

- 1. The VMAX interpreter on the PCMAX2 must be efficient in terms of speed.

- 2. It must be possible to describe VMAX to GCC so that GCC can generate reasonably good code for the machine.

Although considerable care was taken to satisfy these requirements, it is anticipated that the definition of VMAX will be an iterative process. The machine definition will undoubtedly change as experience is gained with GCC and as the interpreter is developed.

#### VMAX Memory and Address Space

The VMAX memory is organized as a flat 32-bit address space of up to 2^32 bytes. The first byte has address 0, and the last byte address 2^32-1. Each byte can be addressed, so in the general case an address requires 32 bits (= 4 bytes). Data operands have no alignment requirements, e.g., a 2-byte word operand need not be word-aligned in memory. However, all instructions must be word-aligned (all instructions occupy an even number of bytes).

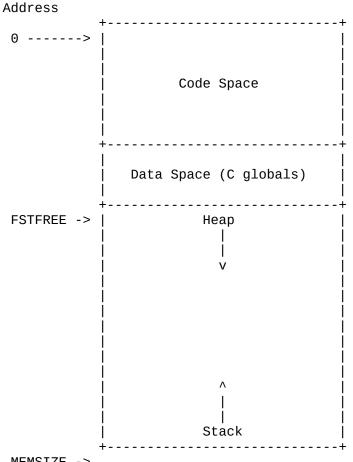

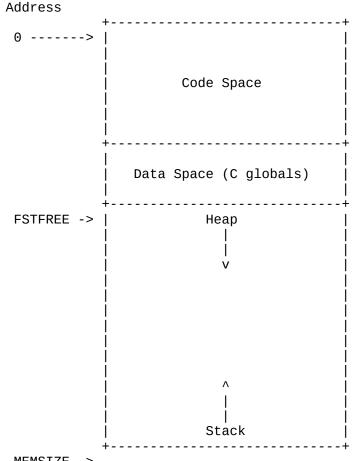

VMAX programs generated by the C compiler organize the VMAX memory like this:

MEMSIZE ->

It should be noted that there is nothing in the VMAX architecture itself which forces the above memory organization (except, perhaps, the fact that the VMAX stack grows from high addresses to low addresses). This organization is very convenient and efficient for programs generated from C

source code, but if one were to write programs directly in VMAX assembly language, it would be possible to intermingle code, data, and the stack in anyway the programmer desired.

The VMAX address space is mapped onto the PCMAX2 Vram: Address zero of VMAX memory is address zero of Vram. Thus the Vram is the VMAX memory.

The VMAX stack begins at the highest available address of Vram and grows downward towards lower addresses.

The VMAX interpreter can use PCMAX2 DataRam in a number of ways: All VMAX registers might be stored in DataRam, or some of them might be stored in PCMAX2 registers. Portions of VMAX memory might be cached in DataRam, e.g., the memory near the current top of the stack, and the memory near the current value of the program counter. However, these are all implementation issues, more or less independent of the definition of VMAX, so no more will be said about them at this time.

One advantage of the mapping from VMAX memory to Vram is that VMAX executable programs do not need to be relocated. They always load at byte zero of Vram.

#### Operand Types

VMAX instructions operate on 9 operand types. The following table lists the types and their corresponding C declarations:

| VMAX data type                                                                                                             | Size (bytes)                                   | C declaration                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| signed byte<br>unsigned byte<br>signed word<br>unsigned word<br>signed long<br>unsigned long<br>float<br>double<br>address | 1<br>1<br>2<br>2<br>4<br>4<br>4<br>4<br>8<br>4 | signed char<br>unsigned char<br>short<br>unsigned short<br>long<br>unsigned long<br>float<br>double<br>pointer to whatever |

|                                                                                                                            |                                                | •                                                                                                                          |

The float and double data types use the standard IEEE 754 formats for single-and double-precision floating-point numbers. All other data types are integer types which are stored in 2's complement form. VMAX is a "little endian" machine, which means that the loworder bytes of a data item are stored at lower addresses than the highorder bytes of the item. In other words, the order of the bytes in memory is opposite to the order in which numbers are usually written. As an example, consider these four bytes stored at memory address A:

|           |         |     | ff | ee | dd | сс  |

|-----------|---------|-----|----|----|----|-----|

|           |         |     |    | Ι  | I  |     |

| stored at | address | А   | +  |    |    |     |

| stored at | address | A+1 |    | -+ |    |     |

| stored at | address | A+2 |    |    | -+ |     |

| stored at | address | A+3 |    |    |    | - + |

The following table shows how these bytes are interpreted when address A appears in an instruction requiring an operand of a specific data type:

| operand type  | order in mem. | usually written a | is value       |

|---------------|---------------|-------------------|----------------|

| signed byte   | ff            | ff                | -1             |

| unsigned byte | ff            | ff                | +255           |

| signed word   | ffee          | eeff              | -4,353         |

| unsigned word | ffee          | eeff              | +61,183        |

| signed long   | ffeeddcc      | ccddeeff          | -857,870,593   |

| unsigned long | ffeeddcc      | ccddeeff          | +3,437,096,703 |

[Note: In this document, unless stated otherwise, numbers are written in the usual order expected by humans, not in the little endian order in which they are actually stored in memory.]

A data item representing an address is the same as an unsigned long. GCC treats the C type "int" as a 32-bit integer, i.e., as a long. Thus there is little mention of "int" in this document, because an "int" is always a long.

As already mentioned, there are no alignment requirements for data operands. An operand may begin at any address in VMAX memory.

#### VMAX Registers

Since GCC is very good at optimizing register usage, VMAX offers a fairly large number of registers:

| general registers<br>8 16-bit word registers:<br>8 32-bit long registers:<br>8 32-bit float registers:<br>8 64-bit double registers: | w0, w1, w2, w3, w4, w5, w6, w7<br>L0, L1, L2, L3, L4, L5, L6, L7<br>f0, f1, f2, f3, f4, f5, f6, f7<br>d0, d1, d2, d3, d4, d5, d6, d7                          |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| other registers<br>1 32-bit program counter:<br>1 16-bit flags register:                                                             | pc<br>flags<br>LUF: less than unsigned flag<br>LF: less than signed flag<br>EF: equal flag<br>GF: greater than signed flag<br>GUF: greater than unsigned flag |

The two long registers L6 and L7 are special in that some instructions use them as implicit operands. Thus, these registers are usually denoted by fp and sp:

fp (= L6) is the frame pointer

sp (= L7) is the stack pointer

The following diagram shows all the VMAX registers:

| ++             | ++              | +       | + +. | +  |

|----------------|-----------------|---------|------|----|

| 0   w0         | 8   L0          | 16   f0 | 24   | d0 |

| 1   w1         | 9   L1          | 17   f1 | 25   | d1 |

| 2   w2  <br>++ | 10   L2         | 18   f2 | 26   | d2 |

| 3   w3  <br>++ | 11   L3         | 19   f3 | 27   | d3 |

| 4   w4         | 12   L4  <br>++ | 20   f4 | 28   | d4 |

| 5   w5         | 13   L5         | 21   f5 | 29   | d5 |

| 6   w6  <br>++ | 14   fp = L6    | 22   f6 | 30   | d6 |

| 7   w7  <br>++ | 15   sp = L7    | 23   f7 | 31   | d7 |

| ++             | ++              | +       | г т· |    |

| ++             | ++              |         |      |    |

| flags          | pc              |         |      |    |

| ++             | ++              |         |      |    |

Note that all registers other than the flags and pc registers are numbered from 0 through 31. This numbering is used in a few instructions which reference registers of any type (most instructions only reference registers of one type).

### General Registers

The decision to provide several types of registers for VMAX was based primarily on the fact that the PCMAX2 is a word machine (word = 2-bytes), which means that operations on operands longer than a word are inherently slower than operations on words. Thus, by providing word registers on the VMAX, operations on C short integers will execute faster than operations on long (4-byte) integers. Also, the new ANSI definition of C allows operands of type float to be operated on with single-precision floating point operations rather than double-precision operations. Thus, when the extra precision of doubles is not needed, speed can be gained by using floats.

VMAX has no byte registers as such. However, individual bytes can be moved to and from the loworder bytes of word and long registers, so all byte operations can be handled. For example, to implement A = B + C, where all three variables are unsigned characters, this VMAX code can be used:

| movbzw | В  | w0 | ; Move byte B zero-extended to word w0  |

|--------|----|----|-----------------------------------------|

| movbzw | С  | w1 | ; Move byte C zero-extended to word w1  |

| addw   | w1 | w0 | ; Add word w1 to w0                     |

| stowb  | w0 | А  | ; Store loworder byte of w0 into byte A |

#### Stack Pointer

Since the primary aim of VMAX is to execute C programs, it is almost imperative that VMAX have a hardware stack. The stack pointer register is an unsigned long register that contains the memory address of the top word in the stack. (The stack grows from high addresses to low addresses, so the "top" of the stack is at a lower address than other elements on the stack.)

Push and pop operations handle variable-length data items, e.g., push word, push long, push float, and push double. A word is the shortest item that can be pushed or popped; there are no instructions to push or pop single bytes.

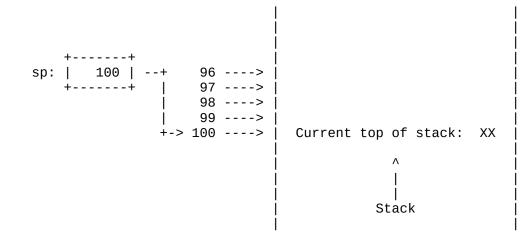

As an example of how the stack pointer changes, consider this situation:

13

The stack pointer contains the value 100, which means that the current top of the stack is at memory address 100. Now say that the instruction

#### pushl 0xccddeeff

is executed to push a long value onto the stack. After this instruction is executed, the stack looks like this:

The pushl operation decrements sp by 4 and moves 4 bytes to the address contained in sp. The inverse operation, popl, fetches the 4 bytes starting with the byte addressed by sp, and then increments sp by 4.

Note that the long value 0xccddeeff is pushed onto the stack with its loworder byte at a lower address than its highorder byte. This is essential to maintain the "little endian" order of operands in memory. Since the VMAX has a flat 32-bit address space, there are no segment registers. In particular, there is no register containing the base of the stack. The stack pointer is an absolute memory address, not an offset relative to some base register. If it is conceptually helpful, the stack can be considered to have a base address of zero.

Frame Pointer

A language like C can be implemented easily enough without a frame pointer, provided that memory can be accessed relative to sp (which is not the case for 80x86 processors). However, GCC seems to require a frame pointer, so VMAX provides one, namely the fp register. This is a 32-bit unsigned long register which usually contains a memory address (almost always the address of something on the stack). Addressing modes exist for accessing operands relative to fp.

To illustrate the use of fp, consider the following C function prototype, definition, and call:

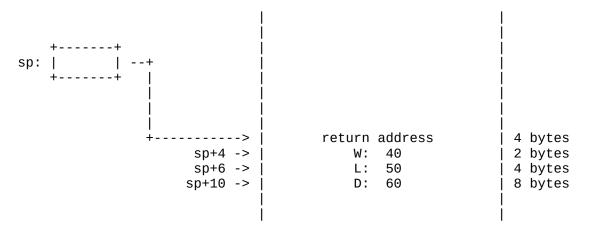

The call of F generates the following VMAX code:

| pushd | 60.0 |    | ; Push third parameter onto stack  |

|-------|------|----|------------------------------------|

| pushl | 50   |    | ; Push second parameter onto stack |

| pushw | 40   |    | ; Push first parameter onto stack  |

| call  | F    |    | ; Call function F                  |

| addl  | 14   | sp | ; Clear parameters from the stack  |

Note that the parameters in the call of F are pushed onto the stack in reverse order, so that the first parameter is at the top of the stack when F is entered. The parameters occupy a total of 14 bytes on the stack (2 for W, 4 for L, and 8 for D), so after the call, sp is incremented by 14 to clear the parameters from the stack. These conventions are usual in C implementations because a function may have a variable number of parameters.

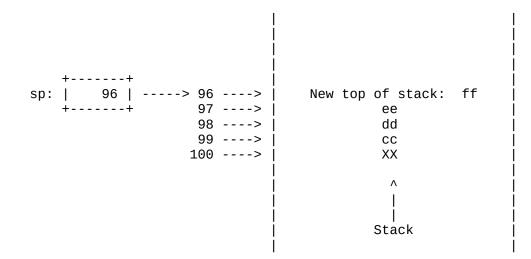

When function F is entered, the stack looks like this:

Here is the code generated for the definition of function F:

| F: | pushl<br>movl<br>subl | fp<br>sp<br>6 | fp<br>sp | ; Save old fp on the stack<br>; Set fp to sp<br>; Reserve stack space for locals |

|----|-----------------------|---------------|----------|----------------------------------------------------------------------------------|

|    | movl<br>popl<br>ret   | fp<br>fp      | sp       | ; Clear locals from the stack<br>; Restore old fp<br>; Return to caller          |

After the subl instruction at the beginning of  ${\sf F}$  is executed, the stack looks like this:

| ++  |            |        |         |   |       |

|-----|------------|--------|---------|---|-------|

| sp: | +          |        |         |   |       |

| ++  | I          |        |         |   |       |

|     | +> fp-6 -> | LA:    | у       | 4 | bytes |

| ++  | fp-2 ->    | WA:    | Х       | 2 | bytes |

| fp: | >          | old    | fp      | 4 | bytes |

| ++  | fp+4 ->    | return | address | 4 | bytes |

|     | fp+8 ->    | W:     | 40      | 2 | bytes |

|     | fp+10 ->   | L:     | 50      | 4 | bytes |

|     | fp+14 ->   | D:     | 60      | 8 | bytes |

|     |            |        |         |   |       |

|     |            |        |         |   |       |

Now, all parameters and local variables of F can be accessed relative to fp. Parameters are accessed with positive offsets, and locals are accessed with negative offsets.

The code at the end of the function clears the local variables from the stack (movl fp sp), restores the old fp (popl fp), and returns to the caller (ret).

A few notes on the preceding:

1. The function prologue and epilogue shown in the example above are not what are actually generated for VMAX. Instead the enter, entersav, leave, and leaveres instructions are used. These instructions perform the same actions as shown in the example, but they require quite a bit fewer bytes of code.

2. Traditional C required that all integer parameters shorter than int in a function call be promoted to int. Thus parameter W in the preceding example would be promoted to an int and pushed onto the stack as 4 bytes instead of as 2 bytes. Similarly, floats were promoted to doubles. However, ANSI C now allows shorts and floats to be passed as they are without promotion (if a prototype for the function specifies the parameters as shorts and floats). The example shown assumes this new standard.

3. Traditional C required that the code for every function be prepared to handle a variable number of arguments. This has changed with ANSI C: If a function prototype does not explicitly indicate that the function takes a variable number of parameters, the compiler can assume that the function takes a fixed number of parameters of fixed types, namely those specified by the prototype. This means that it is now possible for a function to clear its own parameters off the stack, instead of requiring the caller to do this. Although the example above shows the traditional C implementation, GCC will generate code for the new standard when appropriate.

[A note on sp and fp: In the preceding, it has been stated that sp and fp are unsigned long registers. This is not quite correct. In the vast majority of cases sp and fp contain memory addresses, which are unsigned longs. However, all instructions which operate on longs may have either sp or fp as an operand, which means that these two registers are treated like any other long registers. Thus, when it is useful, their contents can be thought of as signed longs.]

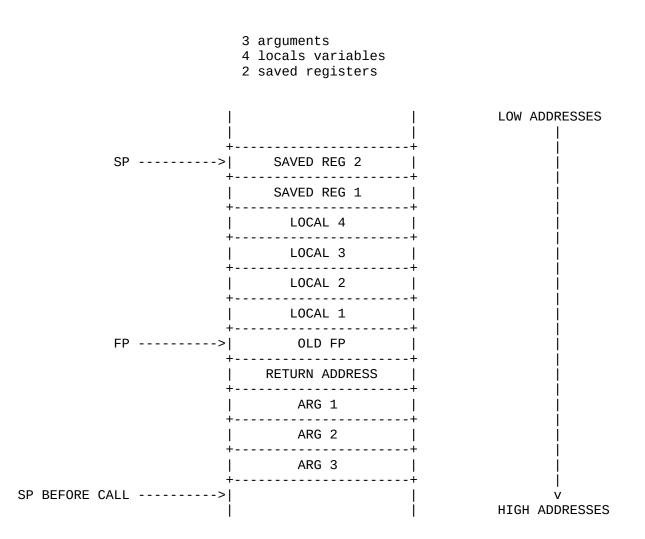

GCC requires that, when necessary, a function preserve certain registers, so part of the function prologue saves registers on the stack. Here is a diagram showing a typical stack frame just after the function prologue has been executed for a function with:

Program Counter

The program counter register, pc, is an unsigned long register which always contains the memory address of the next instruction to execute. The only way this register can be changed under program control is by jump, call, leave, leaveres, and return instructions. Since instructions are always word-aligned and consist of an even number of bytes, the value of pc is always an even number. In addition, when a C program is interpreted, pc must always point to an address in the Code Space (see a figure in an earlier section). Flags Register

The flags register is an unsigned word register whose highorder 11 bits are always zero. The loworder five bits are used to flag various conditions:

| 4       | 3     | 2     | 1     | 0       | L |

|---------|-------|-------|-------|---------|---|

|         |       |       |       |         |   |

| LUF     | LF    | EF    | GF    | GUF     |   |

| < unsgn | < sgn | equal | > sgn | > unsgn |   |

|         |       |       |       |         |   |

Traditionally, computers tend to have a zero flag, a sign flag, an overflow flag, and a carry flag, all of which are changed by many instructions. Because of the nature of the PCMAX2, it would be rather expensive in terms of time to implement this style of flags. Thus, another approach has been taken:

1. The ONLY instructions which change the flags register are compare instructions.

2. Floating point compares set exactly one of the LF, EF, or GF bits, and clear all the others.

3. Integer compares work like this:

If the operands are equal, EF is set and all other flags are cleared.

If the operands are not equal, one of (LF, GF) and one of (LUF, GUF) are set, and all other flags are cleared.

Thus, after an integer compare, it is possible to determine the relationship between the two operands as either signed quantities or unsigned quantities.

This scheme makes it possible to avoid the overhead of setting flag bits after most instructions. Only the compare instructions set the flags. This fits in very well with the way GCC works: It handles conditional branches using the model "compare and branch on the result of the compare".

Of course, the flags scheme described here is not really completely adequate in general. For example, there are no provisions for checking for overflow of arithmetic operations. This is not a problem for GCC because the C language makes no provisions for overflow. However, for general programming it is imperative that some sort of overflow checking be provided on some basis. This will be addressed in a future version of VMAX. [At present VMAX has no control flags for floating point operations. The IEEE 754 floating point standard requires a rather extensive set of control flags, exception flags, etc. These will be added as the VMAX floating point package evolves. Note that we may end up with a flags register of 32 bits rather than 16 bits, or perhaps we will have two flags registers, one for floating point and one for fixed point.]

#### Addressing Modes

The typical VMAX instruction has two operands, one of which is almost always a register. The other operand is a general operand which can be any of the following:

> register immediate operand memory address absolute address of the operand based addressing: base\_register base\_register + displacement indexed addressing: index\_register + displacement based and indexed addressing: base\_register + index\_register

All long registers can be used as both base registers and index registers. When indexing is used, the value of the index register can be scaled by a factor of 1, 2, 4, or 8.

base\_register + index\_register + displacement

The displacements used in based, indexed, and based-indexed addressing modes are of varying lengths. The following list shows the displacement sizes available, and the notation commonly used for these addressing modes:

Based Addressing

| b   | base |   |             |

|-----|------|---|-------------|

| bd1 | base | + | 1-byte-disp |

| bd2 | base | + | 2-byte-disp |

| bd3 | base | + | 3-byte-disp |

| bd4 | base | + | 4-byte-disp |

|     |      |   |             |

# Indexed Addressing

| i   | index |   |             |

|-----|-------|---|-------------|

| id1 | index | + | 1-byte-disp |

| id3 | index | + | 3-byte-disp |

| id4 | index | + | 4-byte-disp |

# Indexed Addressing

| bi   | base + index                          |

|------|---------------------------------------|

| bid2 | base + index + 2-byte-disp            |

| bid4 | <pre>base + index + 4-byte-disp</pre> |

#### Instruction Formats

#### General Considerations

This section discusses the general characteristics of VMAX instructions, as well as the reasons behind the overall design of the instruction formats.

### Instruction length:

All VMAX instructions occupy an even number of bytes; the possible lengths are 2, 4, 6, 8, and 10 bytes (the latter length only occurs when an instruction contains an 8-byte double as an immediate operand). The primary reason that instructions are an even number of bytes long is that the PCMAX2 Vram (where all VMAX instructions are stored) can only be accessed at the word level, not at the byte level. Thus, we increase interpretation speed by using a bit of space (some instructions could be one byte shorter if an odd number of bytes were allowed in an instruction).

## Separate opcode byte:

The first byte of every instruction is an opcode; no other information is encoded in the first byte (although opcodes often imply operand type). Thus, the opcode byte can be used as an index to a jump table in the PCMAX2 DataRam which contains WCS addresses of routines for interpreting opcodes. At present about 145 VMAX opcodes have been defined, and it is anticipated that at most 40 more will be needed. This leaves at least 60 unused opcode values, which allows plenty of leeway for later optimization of the interpreter after experience shows what new instructions would speed up applications.

#### Data types indicated by opcodes:

Instead of encoding operand type information in the operand bytes of an instruction, each opcode operates on a specific data type. Thus, there are four add instructions: Add word, add long, add float, and add double. The format of the operand bytes in these four instructions is identical (except for immediate operands) but the operand bytes describe different types of data depending on the opcode. In effect, type information is carried by the opcode, not by the operand bytes. This allows a more efficient encoding of information in an instruction (see the description of the qr instruction format below).

#### Two-operand instructions:

Most instructions have two operands, one of which is always a register. The other operand is general, i.e., a register, a memory reference, or an immediate operand. Care has been taken to insure that register-to-register instructions are of minimum length, i.e., 2 bytes. For most instructions, both operands have the same type, i.e., both are words, both are longs, etc. However, some instructions exist for converting one type to another, so, of necessity, the two operands are of different types.

## Uniformity:

The instruction formats are fairly uniform, adhering to general schemes with few exceptions. This cuts down on the work needed to interpret the instructions.

[A note on notation: Examples of VMAX instructions in this document are shown in a sort of pseudo assembly language, for example:

| movw | В  | w5 | ; | Move contents of B to w5 |

|------|----|----|---|--------------------------|

| stow | w5 | А  | ; | Store w5 into A          |

Mnemonics for opcodes reflect the actual opcode stored in memory, not what might normally be written in assembly language. For example, in a real assembly language, the single opcode sto might be used instead of stow, stol, stof, and stod. The assembler can figure out which opcode to generate based on the types of the operands.] The VMAX instruction formats are summarized in the following table:

| + -          | +            | +                    | ++                   | +                   | +              |

|--------------|--------------|----------------------|----------------------|---------------------|----------------|

|              | format  <br> | number<br>  operands | first  <br>  operand | second  <br>operand | examples  <br> |

|              | qr           | 2                    | general              | register            | add, move      |

|              | qc           | 2                    | general              | cond. code          | store cond.    |

|              | qo           | 1                    | general              | -                   | push, pop      |

| +-<br> <br>+ | mr           | 2                    | general              | register            | gmov, gsto     |

|              | ir           | 2                    | imm. int             | register            | shift, rotate  |

|              | ij           | 2                    | cond. code           | jump adr            | jump, call     |

|              | a3           | 1                    | 3-byte adr           | -                   | jump, call     |

|              | b1           | 1                    | 1-byte int           | -                   | ret            |

|              | b14          | 2                    | 1-byte int           | 4-byte msk          | entersav       |

| + -          | n0           | 0                    | -                    |                     | halt, nop      |

| +-           | n04          | 1<br>+               | 4-byte msk           | -                   | pushregs       |

|              | = 1          |                      |                      | 1                   | 1              |

## qr-format

Most instructions have the qr-format, in which the q-operand is a general operand (a register, a memory reference, or an immediate value), and the r-operand is a register. The qoperand can involve based addressing, indexed addressing, or both.

## qc-format

This format is used by instructions which store a 0 or a 1 depending on the condition codes. One operand is a general q-operand, and the other specifies a condition.

# qo-format

This is the "q-only" format, i.e., there is only one operand, which is a general q-operand. Push and pop instructions use this format.

#### mr-format

This format is used by only two instructions: gmov and gsto. It includes all the addressing modes of the qr-format except immediate operands, and in addition allows data to be moved regardless of type (for example, 4 word registers can be moved to one double register).

#### ir-format

In this format, one operand is an immediate 5-bit integer, and the other is a register. At present this format is used only by some shift and rotate instructions.

#### ij-format

This format is used by all conditional jump instructions. One operand is a condition, and the other is an address to jump to. Several addressing modes are available for the address.

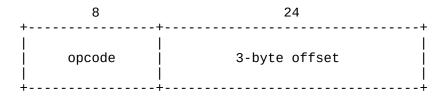

#### a3-format

This format consists of a single operand, a 3-byte memory address. It is used by jump and call instructions.

## b1-format

There is one operand, a 1-byte integer. The enter, leave, and ret and instructions have this format.

#### b14-format

This is the same as the b1-format except that in addition to the 1-byte integer operand there is a 4-byte mask operand. The entersav and leaveres instructions have this format.

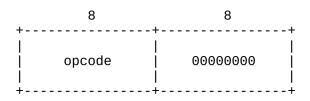

#### n0-format

This is the simplest format there is: There are no operands, only an opcode. An example is nop.

## n04-format

There is one operand, a 4-byte mask. Only the pushregs and popregs instructions have this format.

Each instruction format is described in detail in the following sections.

The qr Format

The qr-format is the most widely used format in the VMAX instruction set. It specifies two operands, a source and a destination, one of which is a general operand, and the other of which is a register.

A qr-format instruction consists of an opcode, a qr-byte, and, for some addressing modes, a sequence of q-bytes.

| 1 byte<br>++       | 1 byte  | 0, 2,<br>+      |      | -    |   | -                   |

|--------------------|---------|-----------------|------|------|---|---------------------|

| <br>  opcode  <br> | qr-byte | <br> <br> <br>+ | q-by | yte: | S | <br> <br> <br> <br> |

The qr-byte consists of two fields, the q-field and the r-field:

| ++<br>  q-field   r-field  <br>  (5 bits)   (3 bits)  <br> |                       | 7 | 6 | 5 | 4 | 3                    | 2 | 1 | 0 |

|------------------------------------------------------------|-----------------------|---|---|---|---|----------------------|---|---|---|

|                                                            | +-<br> <br> <br> <br> |   |   |   |   | +<br> <br> <br> <br> |   |   |   |

The q-field specifies the q-operand, a general operand, and the r-field specifies the r-operand, which is always a register. With a few exceptions, the q-operand is the source operand, and the r-operand is the destination operand. In some cases, e.g., the set of sto instructions which store registers to memory, the r-operand is the source, and the q-operand is the destination.

The sequence of q-bytes which may follow the qr-byte depends on the addressing mode specified in the q-field. All cases are described in detail in following sections.

Since the r-operand is simpler than the q-operand, it is described first.

The r-operand

The register specified by the r-operand is fully determined by two things: The 3-bit integer in the r-field and the operand type implied by the opcode. The following table shows the possible combinations:

| +<br>  r-field<br>  bit | +<br> <br>  decimal · | operand type specified by opcode |      |       |        |  |  |

|-------------------------|-----------------------|----------------------------------|------|-------|--------|--|--|

| pattern                 | value                 | word                             | long | float | double |  |  |

| 000                     | 0                     | w0                               | L0   | f0    | d0     |  |  |

| 001                     | 1                     | w1                               | L1   | f1    | d1     |  |  |

| 010                     | 2                     | w2                               | L2   | f2    | d2     |  |  |

| 011                     | 3                     | w3                               | L3   | f3    | d3     |  |  |

| 100                     | 4                     | w4                               | L4   | f4    | d4     |  |  |

| 101                     | 5                     | w5                               | L5   | f5    | d5     |  |  |

| 110                     | 6                     | w6                               | fp   | f6    | j d6 j |  |  |

| 111                     | 7                     | w7                               | sp   | f7    | d7     |  |  |

| +                       | +                     | +                                |      | +     | ++     |  |  |

As an example, consider this movl (move long) instruction:

| opcode | q-field<br>⊦ | r-field         |  |  |  |

|--------|--------------|-----------------|--|--|--|

| movl   | 00:001       | <br>  110  <br> |  |  |  |

The operand type implied by the opcode is long, so the two registers appearing in the instruction are long registers. Thus the instruction moves the contents of long register 1 to long register 6, i.e., from L1 to fp.

If the opcode is changed to movw (move word), then the registers appearing in the instruction are word registers, so the instruction moves the contents of word register 1 to word register 6, i.e., from w1 to w6.

Note that fp (the frame pointer) and sp (the stack pointer) are long registers. Thus, any instruction that operates on long operands can operate on fp and sp. The q-operand

The q-operand is more complex than the r-operand since it may be a register, an immediate value, or a value in memory accessed via one of several addressing modes. The following options are encoded in the q-field:

|   | 7 | 6 | 5 | 4    | 3 |       |                       |

|---|---|---|---|------|---|-------|-----------------------|

|   | 0 | 0 |   | qreg |   | reg:  | register              |

|   | 0 | 1 |   | Lreg |   | b:    | base register         |

| I | 1 | 0 |   | Lreg |   | bd2:  | base register + disp2 |

|   | 1 | 1 | 0 | 0    | 0 | mema: | memory address        |

|   | 1 | 1 |   | ival |   | imm:  | immediate             |

| ļ | 1 | 1 | 1 | 1    | 1 | regx: | register extended add |

The regx option indicates that there are bytes following the qr-byte which specify the addressing mode. These bytes are described in detail in the following pages.

Before describing each of the q-operand options, some discussion of addresses and values is appropriate.

A q-operand can be either a value or an address. For example, when memory is moved to a register, the q-operand is a VALUE, namely, the contents of a memory location. However, when a register is moved to memory, the q-operand is an ADDRESS, namely, the address of the memory location where the register is to be stored.

For the reg and imm q-operand options, the distinction between values and addresses is not of great importance, because neither registers nor immediate values have addresses (although by stretching things a bit we could probably define some kind of addresses for them).

However, for all other q-operand options, the distinction between values and addresses is important, because these kinds of q-operands are addressing modes. Thus, for each mode the "effective address" is described. For an instruction which requires an address as a q-operand, the effective address is the operand. For an instruction which requires a value as a qoperand, the value stored at the effective address is the operand. The notation EA will be used for "effective address".

Now that the distinction between addresses and values is clear, each of the q-operand options are described in detail:

\* reg: register: q-operand is register contents

The 3-bit qreg field contains an integer which, when combined with the operand type, specifies a register. The encoding is exactly the same as for an r-operand register, as shown in the table for r-operands on a previous page.

\* b: base register: q-operand EA is long register contents

The 3-bit Lreg field contains an integer which specifies any one of the eight long registers, encoded exactly the same as for an r-operand register, as shown in the table for r-operands on a previous page.

The contents of the specified long register is the effective address. As an example of the use of this addressing mode, consider the C statement \*(P+1) = B, where B is a short and P is a pointer to short (both are globals). This can be implemented in VMAX as

| movl | Р  | L3   |              |

|------|----|------|--------------|

| addl | 2  | L3   | ; L3 = P + 1 |

| movw | В  | w0   |              |

| stow | w0 | [L3] | ; *L3 = B    |

Note that both sp and fp can be used in the Lreg field of the base register mode.

> This is the same as the base register mode except that the qr-byte is followed by a signed 2-byte displacement which is added to the contents of the long register specified by Lreg to determine the effective address. Conceptually the displacement is sign-extended to a 4-byte signed value before it is added to the register. (Note: The register contents are NOT changed by this mode.)

As an example, consider the following instruction which stores register w0 to memory. If L3 contains 10, then the instruction stores w0 into memory address 10+2 = 12.

|         |        | •          | qr-byte | -                |

|---------|--------|------------|---------|------------------|

| stow w0 | [L3+2] | <br>  stow |         | <br>  0002  <br> |

\* mema: memory address: q-operand EA is memory address in instruction

The qr-byte is followed by a 4-byte unsigned long which is the effective address. As an example, the following instruction stores register w0 into memory location 65536:

|            | •           | le qr-byt |             | •              |

|------------|-------------|-----------|-------------|----------------|

| stow w0 m6 | 5536   stow | ·<br>     | <br>  0   0 | 00010000  <br> |

\* imm: immediate: q-operand is an immediate value

The 3-bit ival field specifies the immediate value: 001 (imm\_1): -1 010 (imm0): 0 011 (imm1): +1 100 (immv): The immediate value follows the qr-byte 101 (imm2): 2-byte immediate value for long operands

When the immediate value is one of the special values -1, 0, or +1, then there is no need to follow the qr-byte with the value. Thus, the instruction is only 2 bytes long instead of 4 or more bytes. However, the actual operand represented by imm\_1, imm0, or imm1 depends on the operand type specified by the opcode:

| type                                         | imm_1                                                | imm⊙                                               | imm1                                                                 |

|----------------------------------------------|------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------|

| byte:<br>word:<br>long:<br>float:<br>double: | ff<br>ffff<br>ffffffff<br>bf800000<br>bff00000000000 | 00<br>0000<br>00000000<br>00000000<br>000000000000 | 01<br>0001<br>00000001<br>3f800000<br>3ff000000000000000000000000000 |

|                                              |                                                      |                                                    |                                                                      |

Similarly, in the immv case, the immediate value following the qr-byte depends on the operand type:

type immediate operand format byte: 2-byte integer; highorder byte always zero word: 2-byte integer long: 4-byte integer float: 4-byte float double: 8-byte double

Following are examples of immv, in which all types of the immediate value 3 are moved to registers. Note that the qr-bytes of all the instructions are identical, but the byte strings representing the immediate values are different, depending on the operand type indicated by the opcode:

|       |   |    | opcode<br>++      | qr-by1 | te | 2 bytes              |

|-------|---|----|-------------------|--------|----|----------------------|

| movbw | 3 | wO |                   | imm∨   | i  | 0003                 |

|       |   |    | opcode            | qr-by1 | te | 2 bytes              |

| mo∨w  | 3 | wO | <br>  mo∨w  <br>  | imm∨   | 0  | 0003                 |

|       |   |    | opcode            | qr-by1 | te | 4 bytes              |

| movl  | 3 | LO |                   | imm∨   | 0  | <br>  00000003  <br> |

|       |   |    | opcode            | qr-by1 | te | 4 bytes              |

| movf  | 3 | f0 | <br>  movf   <br> | imm∨   | 0  | 40400000  <br>       |

|       |   |    | opcode            | qr-by  | te | 8 bytes              |

| movd  | 3 | d0 | <br>  movd  <br>  | imm∨   | 0  | 4008000000000000000  |

|       |   |    | ++                |        | +  | ++                   |

The imm2 option can only be used with instructions that operate on long data. It indicates that the long immediate value following the qr-byte consists of only 2 bytes. Conceptually these 2 bytes are sign-extended to a 4-byte immediate value. Here is an example of an instruction which moves the value 3 to long register L0:

|      |   |    | •          | qr-byte      | •                |

|------|---|----|------------|--------------|------------------|

| movl | 3 | L0 | <br>  movl | imm2   0<br> | <br>  0003  <br> |

The imm2 option reduces the instruction length from 6 bytes to 4 bytes for many long instructions which have an immediate value.

\* regx: register extended addressing: q-operand specified by x-bytes

The regx option is not really an addressing mode. It is an escape code that indicates that one or two x-bytes follow the qr-byte.

The x-bytes specify one of these addressing modes for the q-operand:

i: index index + disp1 id1: id3: index + disp3 id4: index + disp4 b: base bd1: base + disp1 base + disp3 bd3: bd4: base + disp4 bi: base + index bid2: base + index + disp2 bid4: base + index + disp4

The first byte following the qr-byte is the x1-byte. Bits 4 and 5 of the x1-byte specify the major addressing mode:

| Bits | Meaning                       | Specified by     |  |  |  |  |

|------|-------------------------------|------------------|--|--|--|--|

| 0x   | Index register only           | x1-byte          |  |  |  |  |

| 10   | Base register only            | x1-byte          |  |  |  |  |

| 11   | Both base and index registers | x1- and x2-bytes |  |  |  |  |

The exact bit encoding of each addressing mode is shown in the following diagrams, where this notation is used:

| breg            | A 3-bit base register number (a long register)   |

|-----------------|--------------------------------------------------|

| ireg            | A 3-bit index register number (a long register)  |

| S               | An 2-bit index scale factor                      |

|                 | 00 = 1 (Note: Shifting the index reg.            |

|                 | 01 = 2 left by the number of bits in             |

|                 | 10 = 4 the s field is the same as mul-           |

|                 | <pre>11 = 8 tiplying by the scale factor.)</pre> |

| <0-byte>        | A byte consisting of all zero bits               |

| <dispn></dispn> | An N-byte displacement                           |

| Index Only                      | x1-byte      |                      |                 |  |  |  |

|---------------------------------|--------------|----------------------|-----------------|--|--|--|

| 7                               | 6 5 4 3 2 1  | Θ                    |                 |  |  |  |

| i:   0                          | 0 0   s   ir | eg   <0-byte>        |                 |  |  |  |

| id1:   0                        | 1 0   s   ir | eg   <disp1></disp1> |                 |  |  |  |

| id3:   1                        | 0 0   s   ir | eg   <disp3></disp3> |                 |  |  |  |

| id4:   1                        | 1 0   s   ir | eg   <0-byte>        | <disp4></disp4> |  |  |  |

| +                               |              |                      |                 |  |  |  |

| Base Only:                      | x1-byte      |                      |                 |  |  |  |

| 7                               | 654321       | Θ                    |                 |  |  |  |

|                                 | 0 1 0 0   br |                      |                 |  |  |  |

| bd1:   0                        | 1 1 0 0   br | eg   <disp1></disp1> |                 |  |  |  |

| bd3:   1                        | 0 1 0 0   br | eg   <disp3></disp3> |                 |  |  |  |

| bd4:   1                        | 1 1 0 0   br | eg   <0-byte>        | <disp4></disp4> |  |  |  |

| +                               |              |                      |                 |  |  |  |

| Base and Index: x1-byte x2-byte |              |                      |                 |  |  |  |

|       |   |   |   |   |   |   | 1 |   |   |   |  |   |   |     |   | F |                 |

|-------|---|---|---|---|---|---|---|---|---|---|--|---|---|-----|---|---|-----------------|

| bi:   | 0 | 0 | 1 | 1 | Θ | I |   | 0 | 0 | 0 |  | s | Ι | ire | g |   |                 |

| bid2: | 1 | 0 | 1 | 1 | 0 | I |   | 0 | 0 | 0 |  | s | Ι | ire | g |   | <disp2></disp2> |

| bid4: | 1 | 1 | 1 | 1 | Θ | I |   | 0 | 0 | 0 |  | s | Ι | ire | g |   | <disp4></disp4> |

Note that bits 6 and 7 of the x1-byte specify the displacement and/or 0byte filler needed for each addressing mode. In a sense, bits 6 and 7 are a submode of the major mode specified by bits 4 and 5.

The way in which the effective address of the q-operand is determined for the addressing modes above can be represented by this formula, where B is the contents of the base register, I is the contents of the index register, S is the scale factor, and D is the value of the displacement:

## B + S\*I + sign-extend(D)

This formula works for all the addressing modes if we define B as zero when there is no base register, I as zero when there is no index register, and D as zero when there is no displacement. (Note: A displacement is sign-extended to a 4-byte value before being used in an address calculation.)

[A note on unused bit patterns in the qr-format: The five bits of the q-field can store 32 different bit patterns. At present all bit patterns are used except for one:

#### 11110

The q-field never contains this bit pattern. Also, pattern 11101 (imm2) can only appear in instructions which operate on long data. Numerous bit patterns are not used in the two x-bytes. At some point the unused bit patterns should be listed so that the interpreter can test for them during error checking.]

Notation for qr Operands

In the description of a qr-format instruction, the following notation is used to show what types of operands the instruction takes:

| bvwbyte value (word register)bvlbyte value (long register)wvword valuelvlong valuefvfloat valuedvdouble valuebawbyte address (word register)balbyte address (long register)waword addresslalong address |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>wv word value<br/>lv long value<br/>fv float value<br/>dv double value<br/>baw byte address (word register)<br/>bal byte address (long register)<br/>wa word address</pre>                         |

| Ivlong valuefvfloat valuedvdouble valuebawbyte address (word register)balbyte address (long register)waword address                                                                                     |

| fvfloat valuedvdouble valuebawbyte address (word register)balbyte address (long register)waword address                                                                                                 |

| dvdouble valuebawbyte address (word register)balbyte address (long register)waword address                                                                                                              |

| baw byte address (word register)<br>bal byte address (long register)<br>wa word address                                                                                                                 |

| bal byte address (long register)<br>wa word address                                                                                                                                                     |

| wa word address                                                                                                                                                                                         |

| wa word address                                                                                                                                                                                         |